Elektronik ürünlerin tasarımı şematik diyagramların çizilmesinden PCB düzenine ve kablolamaya kadardır. Bu iş tecrübesi alanındaki bilgi eksikliği nedeniyle sıklıkla çeşitli hatalar meydana gelmekte, takip çalışmalarımızı aksatmakta ve ağır durumlarda yapılan devre kartları hiç kullanılamamaktadır. Bu nedenle bu alandaki bilgimizi geliştirmek için elimizden geleni yapmalı ve her türlü hatadan kaçınmalıyız.

Bu makale, gelecekte aynı çukurlara basılmasını önlemek amacıyla PCB çizim tahtaları kullanıldığında yaygın olarak karşılaşılan delme sorunlarını tanıtmaktadır. Delme; delik, kör delik ve gömülü delik olmak üzere üç kategoriye ayrılır. Açık delikler; geçmeli delikleri (PTH), vida konumlandırma deliklerini (NPTH), kör, gömülü delikleri ve geçiş deliklerini (VIA) içerir; bunların tümü çok katmanlı elektrik iletimi rolünü oynar. Deliğin türü ne olursa olsun, eksik delik sorununun sonucu, ürün grubunun tamamının doğrudan kullanılamamasıdır. Bu nedenle sondaj tasarımının doğruluğu özellikle önemlidir.

PCB Kartlarının Tasarım Tarafındaki Çukurların ve Sızıntıların Durum Açıklaması

Sorun 1: Altium tarafından tasarlanan dosya yuvaları yanlış yerleştirilmiş;

Sorunun açıklaması: Yuva eksik ve ürün kullanılamıyor.

Sebep analizi: Tasarım mühendisi paketi hazırlarken USB aygıtının yuvasını atladı. Tahtayı çizerken bu sorunu bulduğunda, paketi değiştirmedi, ancak doğrudan delik sembolü katmanındaki yuvayı çizdi. Teorik olarak, bu işlemde büyük bir sorun yoktur, ancak üretim sürecinde delme için yalnızca delme katmanı kullanılır, bu nedenle diğer katmanlardaki yuvaların varlığını göz ardı etmek kolaydır, bu da bu yuvanın kaçırılmasına neden olur ve ürün kullanılamaz. Lütfen aşağıdaki resme bakın;

Çukurlardan nasıl kaçınılır: OEM PCB tasarım dosyasının her katmanı, her katmanın işlevine sahiptir. Matkap delikleri ve slot delikleri matkap katmanına yerleştirilmelidir ve tasarımın üretilebileceği düşünülemez.

Soru 2: Altium tasarımlı dosya 0 D kodu ile;

Sorunun açıklaması: Sızıntı açıktır ve iletken değildir.

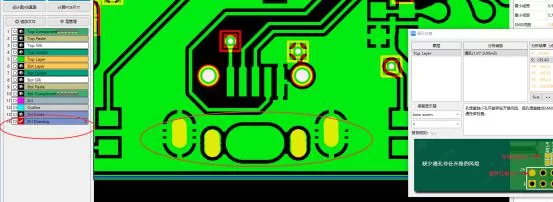

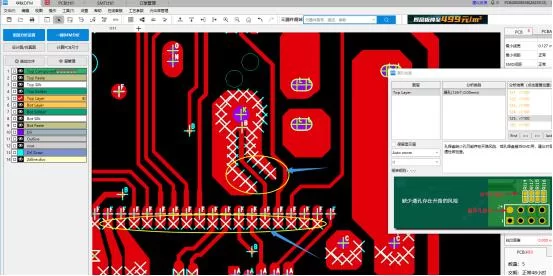

Neden analizi: Lütfen Şekil 1'e bakın, tasarım dosyasında bir sızıntı var ve sızıntı, DFM üretilebilirlik kontrolü sırasında belirtiliyor. Sızıntının nedeni kontrol edildikten sonra Altium yazılımındaki deliğin çapı 0 olur, bu da tasarım dosyasında delik olmamasıyla sonuçlanır, bkz. Şekil 2.

Bu sızıntı deliğinin nedeni tasarım mühendisinin deliği açarken hata yapmış olmasıdır. Bu sızıntı deliğinin sorunu kontrol edilmezse tasarım dosyasında sızıntı deliğini bulmak zorlaşır. Sızıntı deliği elektrik arızasını doğrudan etkiler ve tasarlanan ürün kullanılamaz.

Çukurlardan nasıl kaçınılır: Devre şeması tasarımı tamamlandıktan sonra DFM üretilebilirlik testi yapılmalıdır. Sızdırılan vialar tasarım aşamasında imalat ve üretimde bulunamıyor. Üretimden önce DFM üretilebilirlik testi bu sorunu önleyebilir.

Şekil 1: Tasarım dosyası sızıntısı

Şekil 2: Altium açıklığı 0'dır

Soru 3: PADS tarafından tasarlanan dosya yollarının çıktısı alınamaz;

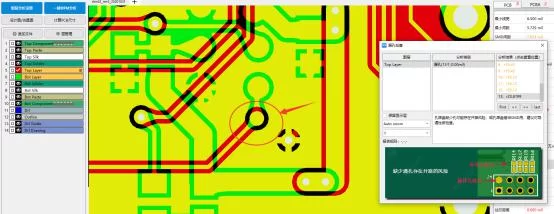

Sorunun açıklaması: Sızıntı açıktır ve iletken değildir.

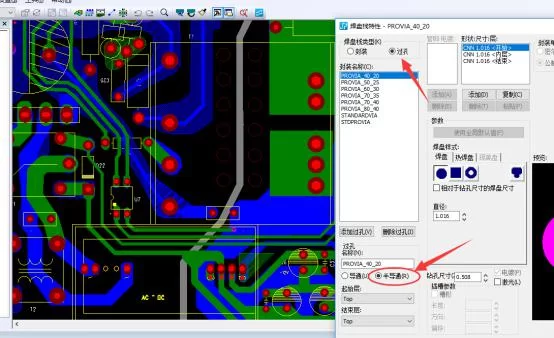

Sebep Analizi: Lütfen Şekil 1'e bakın, DFM üretilebilirlik testini kullanırken bu birçok sızıntıyı gösterir. Sızıntı sorununun nedeni kontrol edildikten sonra, PADS'teki yollardan biri yarı iletken delik olarak tasarlandı, bu da tasarım dosyasının yarı iletken deliğin çıktısını alamamasına ve sızıntıya neden olmasına neden oldu, bkz. Şekil 2.

Çift taraflı panellerde yarı iletken delikler yoktur. Mühendisler tasarım sırasında yanlışlıkla geçiş deliklerini yarı iletken delikler olarak ayarladılar ve çıkış yarı iletken delikleri, çıkış delme sırasında sızdırılarak sızdıran deliklere neden oldu.

Çukurlardan nasıl kaçınılır: Bu tür bir yanlış işlemi bulmak kolay değil. Tasarım tamamlandıktan sonra DFM üretilebilirlik analizi ve muayenesinin yapılması ve sızıntı sorunlarının yaşanmaması için imalat öncesinde sorunların bulunması gerekmektedir.

Şekil 1: Tasarım dosyası sızıntısı

Şekil 2: PADS yazılımı çift panelli geçişler yarı iletken geçişlerdir